半导体洁净解决方案,赋能新质生产力发展

导读

当芯片制程迈入纳米级,洁净室已成为决定良率的核心生产线,而半导体洁净工厂建设技术门槛高、协调难度大、投产周期长等问题,正成为芯片企业的发展掣肘。从ISO洁净标准到半导体“超级工程”,协多利如何为半导体行业构筑极致洁净的防护堡垒?

01

行业痛点

芯片良率的四大“隐形杀手”

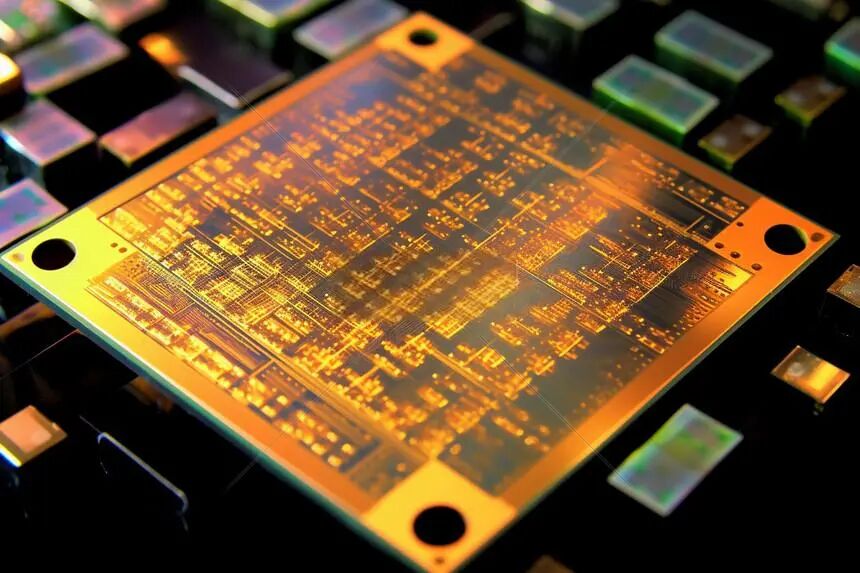

半导体制造的数百道精密工序,对生产环境极为敏感,四大核心痛点直接影响产品良率与可靠性:

微粒污染:0.1μm微粒即可导致晶圆电路短路,传统检测手段难以及时捕捉与拦截;

气态分子污染(AMC):ppb级别的酸碱分子会不可逆地损害光刻胶性能,影响光刻精度与良率;

环境波动:温湿度微小变化可能造成光刻对准偏差,直接影响关键工艺的稳定性;

人为/物流风险:人员操作、物料搬运易引入不可控污染源。

02

协多利硬核技术

精准破解行业洁净难题

针对半导体行业核心痛点,协多利摒弃单一产品供应,以模块化、智能化、绿色化核心技术,打造覆盖“墙、顶、门、窗”的全方位洁净围护系统,从源头解决污染问题,兼顾效率与低碳:

极致密封,从结构上杜绝污染

洁净密封墙板/吊顶采用中置铝型材连接、装配集成安装,无缝隙不积尘,吊顶可满足上人、下挂天车等高负载,适配FFU满布需求,保障高换气次数下的结构稳定。

抗腐防静电,适配严苛工艺

墙板面板可选PVDF材质或导静电处理,耐酸碱腐蚀、抗静电放电(ESD),保护精密元件不受损害。

模块化交付,工期压缩30%以上

所有部件工厂预制、现场仅需装配,减少现场切割污染,大幅缩短施工周期。

绿色低碳,契合双碳目标

产品通过欧、美、日等国际权威认证,优化围护结构气密性,减少冷量流失,降低半导体工厂运营能耗,兼顾环保与成本控制。

专属产品矩阵,为半导体打造洁净“铠甲”

基于核心技术,协多利打造半导体行业专属产品体系,全维度满足高等级洁净室需求,每款产品均贴合半导体制程的核心痛点

03

半导体洁净整体解决方案

筑牢芯片智造高效落地根基

半导体行业的竞争,本质是环境控制能力的竞争。半导体洁净厂房并非简单的工业装修,而是融合多学科的精密工程,其设计与建设需严守国际ISO洁净标准与国家半导体产业规范双重要求,核心围绕纳米级污染控制与环境极致稳定开展。

协多利洁净系统深耕半导体洁净领域多年,聚焦行业洁净痛点,打造覆盖设计—采购—施工—调试—验收—运维的半导体洁净全生命周期整体解决方案,以全链条一体化服务能力,破解芯片产线建设中的技术、工期、协同难题,以180余项专利技术为支撑,覆盖全球50多个国家和地区的服务网络为保障,从国内项目到国际超级工程,始终以专业、创新的姿态,为半导体产业筑牢洁净防线。

结语

“十五五”规划锚定科技自立自强,集成电路居新兴支柱产业首位,AI与算力成为半导体产业升级核心引擎,行业迈入新质生产力发展新阶段。在新质生产力发展的浪潮下,协多利将持续以国际化视野与硬核技术,助力中国半导体迈向更先进制程,与行业伙伴携手,共筑芯片制造的洁净未来!

所有文章未经授权禁止转载、摘编、复制或建立镜像,违规转载法律必究。

举报邮箱:1002263188@qq.com